Implementación VHDL del MBC5

Hacía mucho que no posteaba algún proyecto, pero esto lo merece.

Desde hace un tiempo, llevo pensando en poder prescindir de los chips MBC5 originales de nintendo en mis cartuchos flash para GameBoy, ya que es difícil andar consiguiendo cartuchos antiguos, tiendas de segunda mano, ebay, amigos…

Así que había pensado en reimplementar el MBC5 usando algún chip de lógica programable. El problema es que no tenía conocimientos sobre ello :-)

Así que me puse a diseñar el funcionamiento del MBC5 en puertas lógicas, usando el Ktechlab, hasta que tuve algo que más o menos se comportaba como debía, asi que entonces ya me empezé a plantear en hacer un diseño definitivo.

Buscando encontré la gama XC9500 de Xilinx, CPLDs pequeños de 5V, con el más simple de todos, el XC9536, en formato TQFP de 44 pines, muy similar al MBC5 de 32 pines, que podria adaptar fácilmente a mi cartucho. Asi que me puse manos a la obra. Amazon y a buscar un libro de VHDL. Encontré de segunda mano «Digital Design, an embedded systems approach using VHDL» a buen precio, asi, que lo compré, y me está resultando una buena lectura, muy recomendable. Una vez aprendido lo básico, ya me puse a jugar con un kit de desarrollo CoolRunnerII que tenemos en el LABee, y cogiendo algo de soltura. Asi que un dia me puse a escribir líneas de VHDL y este fin de semana, más o menos he dejado el diseño listo.

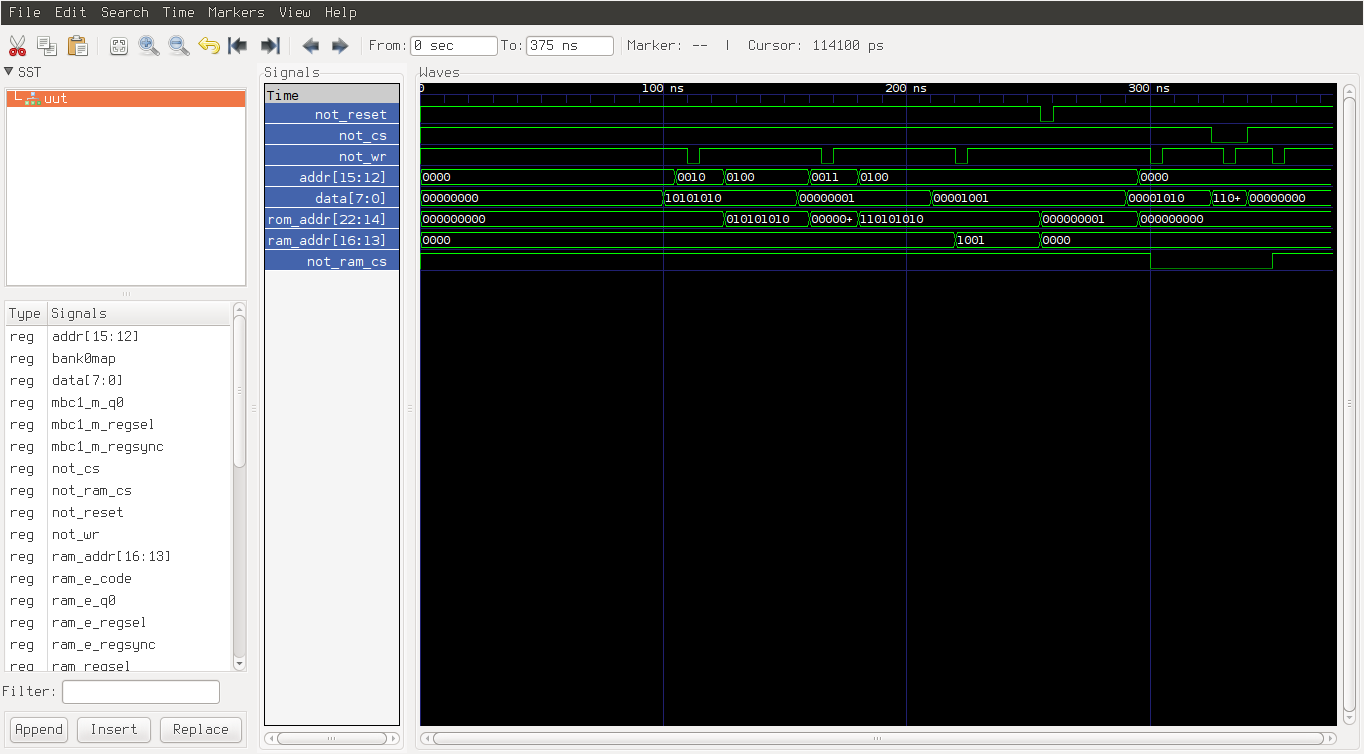

En la captura podeis ver la simulación de mi implementación del MBC5 funcionando, pruebo todos los modos posibles, selección de bancos ROM bajo, ROM alto, bancos de RAM, activación y desactivación de la RAM externa, escritura en la RAM externa, reset… todo parece funcionar según el diseño original del MBC5. Lo único que he cambiado es el mapeado del banco 0 para la compatibilidad con el MBC1. El MBC5 permite mapear el banco 0 en el segundo banco de ROM físico del cartucho a partir de 4000h, mientras que el MBC1, si le pedimos seleccionar el banco 0, nos pondrá el banco 1 en 4000H. No conozco ningún juego o programa que mapee el banco 0 en 4000h, asi que creo que es más interesante usar el formato del MBC1 y asi evitar incompatibilidades con programas antiguos.

Con el ISE de xilinx, ya he sintetizado el diseño, seleccionado los pines para la E/S y dejado todo listo para cuando me lleguen los CPLD’s que tengo pedidos y el JTAG USB de xilinx. En seguida podré probarlo en hardware real y a ver que pasa.

Ahora que he empezado con la lógica programable, me va a ser difícil parar, esto es demasiado interesante y útil como para no hacer más cosas :-)

En cuanto tenga todo comprobado publicaré los fuentes VHDL de mi diseño. Además tengo pensado hacerle unos añadidos, ya que me sobran dos o tres pines… más ROM? más RAM?, I/O? ya veremos ;-)